譯碼是編碼的反過程。編碼是將信號轉換成二進制代碼,譯碼則是將二進制代碼轉換成特定的信號。將輸入的二進制代碼轉換成特定的高(低)電平信號輸出的邏輯電路稱為譯碼器。

假設譯碼器由n個輸入信號和N個輸出信號,如果滿足N=2n,就稱為全譯碼器,又稱二進制譯碼器,常見的全譯碼器由2-4線譯碼器、3-8線譯碼器、4-16線譯碼器等。如果滿足N<2n,稱為部分譯碼器,如二-十進制譯碼器(又稱4-10譯碼器)、顯示譯碼器等。

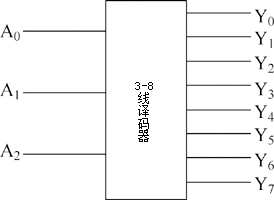

3-8線譯碼器是一種全譯碼器(二進制譯碼器)。全譯碼器的輸入是3位二進制代碼,3位二進制代碼共有8種組合,故輸出是與這8種組合一一對應的8個輸出信號。譯碼器將每種二進制的代碼組合譯成對應的一根輸出線上的高(低)電平信號。因此這種譯碼器也稱為3-8線譯碼器。圖5-44時5-6-1線譯碼器的框圖。

|

| 圖1 3-8線譯碼器框圖 |

根據3-8線譯碼器的邏輯功能可以列出它的邏輯真值表,如表1所示。

從表1中所示可以看出,輸入信號的每一種組合對應著一個輸出端的高電平信號,即輸出端為高電平(1)時認為該輸出端有輸出信號。當然,根據有需要也可以定義輸出端為低電平(0)時認為該輸出端有輸入信號,此時稱輸出端低電平有效。

表1 3-8線譯碼器的邏輯真值表

| 輸入 | 輸出 | |||||||||

| A2 | A1 | A0 | Y7 | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

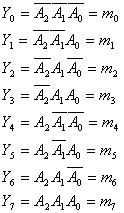

根據真值表可以寫出邏輯函數式為

|

(1) |

根據邏輯函數式可以畫出3-8線譯碼器的邏輯電路,如圖2所示。

|

| 圖2 3.8線譯碼器的邏輯電路圖 |

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底