öĄųĄ▒╚▌^Ų„Š═╩Ūī”ā╔éĆöĄAĪóB▀Mąą▒╚▌^Ż¼ęį▒Ń┼ąöÓŲõ┤¾ąĪĄ─▀ē▌ŗļŖ┬ĘĪŻ

ę╗Īó1╬╗öĄųĄ▒╚▌^Ų„

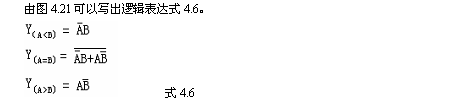

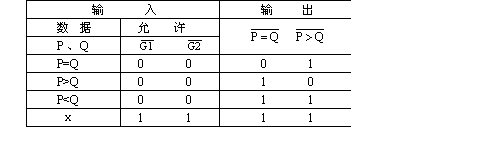

łD4.21╩Ū1╬╗öĄųĄ▒╚▌^Ų„Ą─▀ē▌ŗłDĪŻ╦³ėąā╔éĆ▌ö╚ļČ╦Ż¼Ęųäe▌ö╚ļöĄųĄA║═öĄųĄBĪŻā╔éĆöĄųĄ▀Mąą▒╚▌^Ģrėą╚²ĘNĮY╣¹Ż║A>BĪóA=Bęį╝░A<BĪŻ╦∙ęį╦³ėą╚²éĆ▌ö│÷Č╦ĪŻ

łD4.21 1╬╗öĄųĄ▒╚▌^Ų„

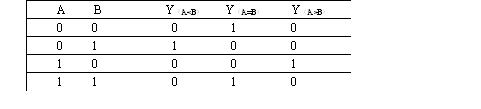

Ė∙ō■▀ē▌ŗ▒Ē▀_╩Į4.6┐╔ęį┴ą│÷šµųĄ▒Ē╚ń▒Ē4.12╦∙╩ŠĪŻ

▒Ē4.12 1╬╗öĄųĄ▒╚▌^Ų„šµųĄ▒Ē

ė╔▒Ē4.12┐╔ęį┐┤│÷Ż¼«öA<B Ż©A=0Ż¼B=1Ż® Ģrų╗ėąY(A<B)ŻĮ1Ż¼ŲõėÓ▌ö│÷Č╦×ķĪ░0Ī▒Ż╗«öA=BŻ©A=0Ż¼B=0║═A=1Ż¼B=1Ż®ĢrY(A=B)=1Ż╗«öA>B Ż©A=1Ż¼B=0Ż® ĢrY(A>B)=1ĪŻįōļŖ┬Ę┐╔ęįĖ∙ō■▌ö│÷Č╦Ą─▀ē▌ŗĀŅæBŻ¼┼ąöÓ│÷▌ö╚ļĄ─ā╔éĆ1╬╗Č■▀MųŲöĄAĪóBĄ─┤¾ąĪĪŻ═Ļ│╔Ą─╩Ū1╬╗öĄųĄ▒╚▌^Ą─▀ē▌ŗ╣”─▄Ż¼╦∙ęį╦³╩Ū1╬╗öĄųĄ▒╚▌^Ų„ĪŻį┌īŹļHæ¬ė├ųą═∙═∙ąĶę¬▒╚▌^ā╔éĆČÓ╬╗Č■▀MųŲöĄŻ¼Š═ąĶę¬░č╔Ž├µĄ─1╬╗öĄųĄ▒╚▌^Ų„║Ž└ĒĄ─▀BĮėŲüĒ╩╣ė├Ż¼ĮM│╔ČÓ╬╗öĄųĄ▒╚▌^Ų„

«öā╔éĆČÓ╬╗Č■▀MųŲöĄąĶę¬▒╚▌^ĢrŻ¼æ¬įōÅ─Ė▀╬╗ĄĮĄ═╬╗Ż¼ų╬╗▀Mąą▒╚▌^Ż¼Č°Ūęų╗ėą«öĖ▀╬╗ŽÓĄ╚ĢrŻ¼▓┼ėą▒žę¬▒╚▌^ŽÓÓÅĄ─Ą═ę╗╬╗Ż¼ę╗ų▒ĄĮūŅĄ═ę╗╬╗ĪŻ└²╚ńā╔éĆ4╬╗Č■▀MųŲöĄŻ¼A=A3A2A1A0ĪóB=B3B2B1B0▀Mąą▒╚▌^ĢrŻ¼╚ń╣¹A3>B3šf├„A>BŻ╗╚ń╣¹A3<B3šf├„A<BŻ╗ų╗ėą«öA3=B3ĢrŻ¼ąĶę¬▒╚▌^A2║═B2Ż¼░┤┤╦ĘĮĘ©Å─Ė▀╬╗ĄĮĄ═╬╗ę└┤╬▀Mąą▒╚▌^Ż¼╝┤┐╔ęįĄ├│÷ūŅ║¾Ą─▒╚▌^ĮY╣¹ĪŻ░┤šš┤╦╦╝┬ĘįOėŗ│÷Ą─ųąęÄ─ŻöĄųĄ▒╚▌^Ų„ėąČÓĘNĪŻ└²╚ń74LS521Īó74LS686 ×ķ8╬╗öĄųĄ▒╚▌^Ų„ĪóCC4585×ķ4╬╗öĄųĄ▒╚▌^Ų„Ą╚Ą╚ĪŻłD4.22Ż©aŻ®×ķ74LS686╣▄─_┼┼┴ąłDŻ¼łD4.22Ż©bŻ®×ķCC4585╣▄─_┼┼┴ąłDĪŻ74LS686╣”─▄▒Ē╚ń▒Ē4.13╦∙╩ŠĪŻ

łD4.22 öĄųĄ▒╚▌^Ų„╣▄─_┼┼┴ąłD

▒Ē4.13 74LS686╣”─▄▒Ē

174LS686┐╔ęįī”ā╔éĆ8╬╗öĄ▀Mąąų╬╗▒╚▌^ĪŻė╔▒Ē4.13┐╔ęį┐┤│÷Ż¼«öP=Q▌ö│÷Č╦×ķĄ═ļŖŲĮĢr▒Ē╩Šā╔éĆ8╬╗öĄ═Ļ╚½ŽÓĄ╚Ż╗«öP>Q▌ö│÷Č╦×ķĄ═ļŖŲĮĢr▒Ē╩ŠP8╬╗öĄ┤¾ė┌Q8╬╗öĄŻ╗«öā╔éĆ▌ö│÷Č╦Č╝▌ö│÷Ė▀ļŖŲĮŻ©╝┤▓╗ŽÓĄ╚Ż¼ę▓▓╗┤¾ė┌Ż®Ģr▒Ē╩ŠP8╬╗öĄąĪė┌Q8╬╗öĄĪŻ

G1║═G2 ×ķ┐žųŲČ╦Ż¼Ą═ļŖŲĮėąą¦ĪŻ╝┤G1 ŻĮ G2ŻĮ0Ģr▒╚▌^Ų„š²│Ż╣żū„Ż¼ G1 ŻĮ G2 ŻĮ1Ģr▒╚▌^Ų„▓╗╣żū„ĪŻ

łD4.22Ż©bŻ®ųąĄ─CC4585×ķ4╬╗öĄųĄ▒╚▌^Ų„ĪŻ×ķ┴╦öUš╣▀ē▌ŗ╣”─▄Ż¼įOėŗ┴╦Ą═╬╗▒╚▌^▌ö╚ļČ╦ĪŻā╚▓┐ĮYśŗę¬Ū¾Ż¼ų╗▒╚▌^ā╔éĆ4╬╗öĄĢrŻ¼ę¬Ū¾Ī░▌ö╚ļA<BĪ▒ŻĮ0ĪóĪ░▌ö╚ļAŻĮBĪ▒ŻĮ1ĪóĪ░▌ö╚ļA>BĪ▒ŻĮ1ĪŻ

ĘĄ╗žĒö▓┐

ĘĄ╗žĒö▓┐ ╦óą┬Ēō├µ

╦óą┬Ēō├µ Ž┬ĄĮĒōĄū

Ž┬ĄĮĒōĄū