ĪĪĪĪŪ░├µĘų╬÷ĮM║Ž▀ē▌ŗļŖ┬ĘĢrŻ¼Č╝ø]ėą┐╝æ]ķTļŖ┬ĘĄ─čė▀tĢrķgī”ļŖ┬Ę«a╔·Ą─ė░ĒæĪŻīŹļH╔ŽŻ¼Å─ą┼╠¢▌ö╚ļĄĮĘĆČ©▌ö│÷ąĶę¬ę╗Č©Ą─ĢrķgĪŻė╔ė┌Å─▌ö╚ļĄĮ▌ö│÷Ą─▀^│╠ųąŻ¼▓╗═¼═©┬Ę╔ŽķTĄ─╝ēöĄ▓╗═¼Ż¼╗“š▀ķTļŖ┬ĘŲĮŠ∙čė▀tĢrķgĄ─▓Ņ«ÉŻ¼╩╣ą┼╠¢Å─▌ö╚╦Įø▓╗═¼═©┬Ęé„▌öĄĮ▌ö│÷╝ēĄ─Ģrķg▓╗═¼

ĪŻė╔ė┌▀@éĆįŁę“Ż¼┐╔─▄Ģ■╩╣▀ē▌ŗļŖ┬Ę«a╔·Õeš`▌ö│÷ĪŻ═©│Ż░č▀@ĘN¼FŽ¾ĘQ×ķĖéĀÄ├░ļUĪŻ

ę╗Īó«a╔·ĖéĀÄ├░ļUĄ─įŁę“

ĪĪĪĪ╩ūŽ╚üĒĘų╬÷Ž┬łD╦∙╩ŠļŖ┬ĘĄ─╣żū„ŪķørŻ¼┐╔ęįĮ©┴óĖéĀÄ├░ļUĄ─Ė┼─Ņ

ĪŻ

ĪĪ

ĪĪ

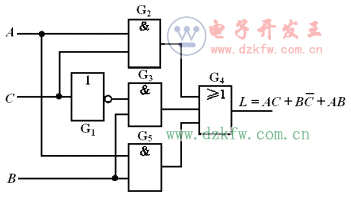

ĪĪĪĪį┌łDųąŻ¼┼cķTG2Ą─▌ö╚ļ╩ŪŻ┴║═ ā╔éĆ╗źčaą┼╠¢ĪŻė╔ė┌G1Ą─čė▀tŻ¼

ā╔éĆ╗źčaą┼╠¢ĪŻė╔ė┌G1Ą─čė▀tŻ¼ Ą─Ž┬ĮĄčžę¬£■║¾ė┌Ż┴Ą─╔Ž╔²čžŻ¼ę“┤╦į┌║▄Č╠Ą─ĢrķgķgĖ¶ā╚Ż¼G2Ą─ā╔éĆ▌ö╚ļČ╦Č╝Ģ■│÷¼FĖ▀ļŖŲĮŻ¼ų┬╩╣╦³Ą─▌ö│÷│÷¼Fę╗éĆĖ▀ļŖŲĮšŁ├}ø_Ż©╦³╩Ū░┤▀ē▌ŗįOėŗę¬Ū¾▓╗æ¬│÷¼FĄ─Ė╔ö_├}ø_Ż®Ż¼ęŖłDųąĄ─▓©ą╬▓┐Ęų╦∙╩ŠĪŻ┼cķTG2Ą─Ż▓éĆ▌ö╚ļą┼╠¢Ęųäeė╔G1║═Ż┴Č╦ā╔éĆ┬ĘÅĮį┌▓╗═¼Ą─Ģr┐╠ĄĮ▀_Ą─¼FŽ¾Ż¼═©│ŻĘQ×ķĖéĀÄŻ¼ė╔┤╦Č°«a╔·▌ö│÷Ė╔ö_├}ø_Ą─¼FŽ¾ĘQ×ķ├░ļUĪŻ

Ą─Ž┬ĮĄčžę¬£■║¾ė┌Ż┴Ą─╔Ž╔²čžŻ¼ę“┤╦į┌║▄Č╠Ą─ĢrķgķgĖ¶ā╚Ż¼G2Ą─ā╔éĆ▌ö╚ļČ╦Č╝Ģ■│÷¼FĖ▀ļŖŲĮŻ¼ų┬╩╣╦³Ą─▌ö│÷│÷¼Fę╗éĆĖ▀ļŖŲĮšŁ├}ø_Ż©╦³╩Ū░┤▀ē▌ŗįOėŗę¬Ū¾▓╗æ¬│÷¼FĄ─Ė╔ö_├}ø_Ż®Ż¼ęŖłDųąĄ─▓©ą╬▓┐Ęų╦∙╩ŠĪŻ┼cķTG2Ą─Ż▓éĆ▌ö╚ļą┼╠¢Ęųäeė╔G1║═Ż┴Č╦ā╔éĆ┬ĘÅĮį┌▓╗═¼Ą─Ģr┐╠ĄĮ▀_Ą─¼FŽ¾Ż¼═©│ŻĘQ×ķĖéĀÄŻ¼ė╔┤╦Č°«a╔·▌ö│÷Ė╔ö_├}ø_Ą─¼FŽ¾ĘQ×ķ├░ļUĪŻ

ĪĪĪĪŽ┬├µ▀Mę╗▓ĮĘų╬÷ĮM║Ž▀ē▌ŗļŖ┬Ę«a╔·ĖéĀÄ├░ļUĄ─įŁę“ĪŻ

ĪĪĪĪįOėąę╗éĆ▀ē▌ŗļŖ┬Ę╚ń╔ŽłD╦∙╩ŠŻ¼Ųõ╣żū„▓©ą╬╚ńŽ┬łD╦∙╩ŠĪŻ╦³Ą─▌ö│÷▀ē▌ŗ▒Ē▀_╩Į×ķ ĪŻė╔┤╦╩Į┐╔ų¬,«öŻ┴║═Ż┬Č╝×ķ1ĢrŻ¼LŻĮ1Ż¼┼cCĄ─ĀŅæB¤oĻPĪŻĄ½╩ŪŻ¼ė╔▓©ą╬łD┐╔ęį┐┤│÷Ż¼į┌Ż├ė╔Ż▒ūāŻ░ĢrŻ¼Ż├ė╔Ż░ūāŻ▒ėąę╗čė▀tĢrķgŻ¼į┌▀@éĆĢrķgķgĖ¶ā╚,G2║═G3Ą─▌ö│÷Ż┴Ż├║═

ĪŻė╔┤╦╩Į┐╔ų¬,«öŻ┴║═Ż┬Č╝×ķ1ĢrŻ¼LŻĮ1Ż¼┼cCĄ─ĀŅæB¤oĻPĪŻĄ½╩ŪŻ¼ė╔▓©ą╬łD┐╔ęį┐┤│÷Ż¼į┌Ż├ė╔Ż▒ūāŻ░ĢrŻ¼Ż├ė╔Ż░ūāŻ▒ėąę╗čė▀tĢrķgŻ¼į┌▀@éĆĢrķgķgĖ¶ā╚,G2║═G3Ą─▌ö│÷Ż┴Ż├║═ ═¼Ģr×ķŻ░Ż¼Č°╩╣▌ö│÷│÷¼Fę╗žō╠°ūāĄ─šŁ├}ø_Ż¼╝┤├░ļU¼FŽ¾ĪŻ▀@╩Ū«a╔·ĖéĀÄ├░ļUĄ─įŁę“ų«ę╗Ż¼Ųõ╦¹įŁę“▀@└’▓╗ū„įö╩÷ĪŻ

═¼Ģr×ķŻ░Ż¼Č°╩╣▌ö│÷│÷¼Fę╗žō╠°ūāĄ─šŁ├}ø_Ż¼╝┤├░ļU¼FŽ¾ĪŻ▀@╩Ū«a╔·ĖéĀÄ├░ļUĄ─įŁę“ų«ę╗Ż¼Ųõ╦¹įŁę“▀@└’▓╗ū„įö╩÷ĪŻ

ĪĪĪĪė╔ęį╔ŽĘų╬÷┐╔ų¬Ż¼«öļŖ┬Ęųą┤µį┌ė╔Ę┤ŽÓŲ„«a╔·Ą─╗źčaą┼╠¢Ż¼Ūęį┌╗źčaą┼╠¢Ą─ĀŅæB░l╔·ūā╗»Ģr┐╔─▄│÷¼F├░ļU¼FŽ¾

Č■ĪóŽ¹╚źĖéĀÄ├░ļUĄ─ĘĮĘ©

ĪĪĪĪßśī”╔Ž╩÷įŁę“Ż¼┐╔ęį▓╔╚ĪęįŽ┬┤ļ╩®Ž¹╚źĖéĀÄ├░ļU¼FŽ¾ĪŻ

1.░l¼F▓óŽ¹Ą¶╗źčaūā┴┐

ĪĪĪĪ└²╚ńŻ¼║»öĄ╩Į Ż¼į┌Ż┬ŻĮŻ├ŻĮŻ░ĢrŻ¼

Ż¼į┌Ż┬ŻĮŻ├ŻĮŻ░ĢrŻ¼

ĪŻ╚¶ų▒ĮėĖ∙ō■▀@éĆ▀ē▌ŗ▒Ē▀_╩ĮĮM│╔▀ē▌ŗļŖ┬ĘŻ¼ät┐╔─▄│÷¼FĖéĀÄ├░ļUĪŻ┐╔ęįīóįō╩ĮūāōQ×ķ Ż¼▀@└’ęčīó

Ż¼▀@└’ęčīó Ž¹Ą¶ĪŻĖ∙ō■▀@éĆ▒Ē▀_╩ĮĮM│╔▀ē▌ŗļŖ┬ĘŠ═▓╗Ģ■│÷¼FĖéĀÄ├░ļUĪŻ

Ž¹Ą¶ĪŻĖ∙ō■▀@éĆ▒Ē▀_╩ĮĮM│╔▀ē▌ŗļŖ┬ĘŠ═▓╗Ģ■│÷¼FĖéĀÄ├░ļUĪŻ

2.į÷╝ė│╦ĘeĒŚ

ĪĪĪĪī”ė┌Ž┬łDųą╦∙╩ŠĄ─▀ē▌ŗļŖ┬Ę(a)Ż¼┐╔ęįĖ∙ō■▀ē▌ŗ┤·öĄųąĄ─│Żė├║ŃĄ╚╩ĮŻ¼į┌Ųõ▌ö│÷▀ē▌ŗ▒Ē▀_╩Įųąį÷╝ė│╦ĘeĒŚABĪŻ▀@ĢrŻ¼

Ż¼ī”æ¬Ą─▀ē▌ŗļŖ┬Ę╚ńłD(b)╦∙╩ŠĪŻė╔Ū░├µĄ─Ęų╬÷┐╔ų¬Ż¼│÷¼Fžō╠°ūāšŁ├}ø_╠ÄŻ¼š²╩ŪŻ┴║═Ż┬Š∙×ķŻ▒ĢrĪŻ’@╚╗Ż¼ī”ė┌łD(b)╦∙╩ŠļŖ┬ĘŻ¼«öŻ┴ŻĮŻ┬ŻĮŻ▒ĢrŻ¼G5▌ö│÷×ķŻ▒Ż¼G4▌ö│÷ęÓ×ķŻ▒Ż¼▀@Š═Ž¹│²┴╦C╠°ūāĢrī”▌ö│÷ĀŅæBĄ─ė░ĒæŻ¼Å─Č°Ž¹╚ź┴╦ĖéĀÄ├░ļUĪŻ

(a)

(b)

3. ▌ö│÷Č╦▓ó┬ōļŖ╚▌Ų„

ĪĪĪĪ╚ń╣¹▀ē▌ŗļŖ┬Ęį┌▌^┬²╦┘Č╚Ž┬╣żū„Ż¼×ķ┴╦Ž¹╚źĖéĀÄ├░ļUŻ¼┐╔ęįį┌▌ö│÷Č╦▓ó┬ōĪ¬Ī¬ļŖ╚▌Ų„Ż¼Ųõ╚▌┴┐×ķ4Ī½20pFų«ķg,▒╚╚ń┐╔ęįį┌ėęłDĄ─ļŖ┬ĘĄ─▌ö│÷Č╦▓ó┬ōę╗éĆļŖ╚▌Ż├Ż¼╚ńŽ┬łD╦∙╩ŠĪŻė╔ė┌╗“ķTG4┤µį┌Ī¬Ī¬▌ö│÷ļŖūĶR0Ż¼ų┬╩╣▌ö│÷▓©ą╬╔Ž╔²čž║═Ž┬ĮĄčžĄ─ūā╗»ūāĄ├▒╚▌^ŠÅ┬²ĪŻę“┤╦ī”ė┌║▄šŁĄ─žō╠°ūā├}ø_ŲĄĮŲĮ╗¼Ą─ū„ė├Ż¼╚ńŽ┬łDųąĄ─▓©ą╬╦∙╩ŠĪŻ’@╚╗Ż¼▀@Ģrį┌▌ö│÷Č╦▓╗Ģ■│÷¼F▀ē▌ŗÕeš`ĪŻ

ĘĄ╗žĒö▓┐

ĘĄ╗žĒö▓┐ ╦óą┬Ēō├µ

╦óą┬Ēō├µ Ž┬ĄĮĒōĄū

Ž┬ĄĮĒōĄū