數字電路分為組合邏輯電路和時序邏輯電路兩類,組合邏輯電路的特點是輸出信號只是該時的輸入信號的函數,與別時刻的輸入狀態無關,它是無記憶功能的。這一章我們來學習組合邏輯電路。這一章是本課程的重點內容之一

我們在學習時把這一章的內容分為:

§4、1 邏輯電路的分析

§4、2 邏輯電路的設計

§4、3 常用的組合邏輯

§4、1 組合邏輯電路的分析

一:組合邏輯電路的分析 (1):有給定的邏輯電路圖,寫出輸出端的邏輯表達式; (2):列出真值表; (3):通過真值表概括出邏輯功能,看原電路是不是最理想,若不是,則對其進行改進;

我們對組合邏輯電路的分析分以下幾個步驟:

。 第一步:寫邏輯表達式。我們由前級到后級寫出各門邏輯表達式

例1:已知右面的邏輯電路圖,試分析其功能。

P=A+B S=A+P=AB W=B+P=AB

F=S+W=AB+A B

第二步:列真值表(如右圖所示)。

第三步:邏輯功能描述并改進設計。

從真值表中可以看出這是一個二變量“同或”電路。原電路設計不合理,它只需一個"同或"門即可.

§4、2 組合邏輯電路的設計

一:組合電路邏輯電路的設計

電路設計的任務就是根據功能設計電路,一般按如下的步驟進行:

(1)把邏輯命題換為真值表;這一步我們要從以下幾個反面考慮

用英文字母代表輸入或輸出;

分清幾個輸入、輸出;

分清輸入和輸出之間的對應關系。

(2)把邏輯函數進行化簡,化簡的形式則是根據所選用的邏輯門來決定;

(3)根據化簡結果和所選定的門電路,畫出邏輯電路圖。

例: 設計三變量表決器,其中X具有否決權。

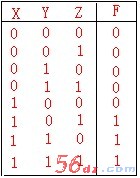

第一步:列出真值表。(如右上圖)

設X、Y、Z分別代表參加表決的變量;F為表決結果,

我們把變量規定為:X、Y、Z為1表示贊成;為0表示反對。

F為1表示通過;為0表示被否決。

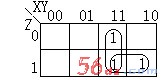

第二步:化簡邏輯函數。

我們選用與非邏輯來實現。用卡諾圖來化簡(如右中圖)F=![]()

第三步:畫邏輯電路。(如右圖)

§4、3 常用的組合邏輯

常用組合邏輯的種類很多,主要有全加器、譯碼器、編碼器、多路選擇器等,下面我們分別把它們介紹一下。

一:半加器和全加器

在數字系統中算術運算都是利用加法進行的,因此加法器是數字系統中最基本的運算單元。由于二進制運算可以用邏輯運算來表示,因此我們可以用邏輯設計的方法來設計運算電路。加法在數字系統中分為全加和半加(第一章我們已經介紹了)所以加法器也分為全加器和半加器。

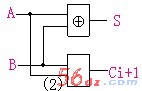

(1)半加器設計

半加器不考慮低位向本位的進位,因此它有兩個輸入端和兩個輸出端。

設加數(輸入端)為A、B ;和為S ;向高位的進位為Ci+1。

它的真值表為:如右圖所示

函數的邏輯表達式為: S=AB+AB ; Ci+1=AB

邏輯電路圖(用異或門和與門構成)為:如右圖(2)所示

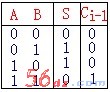

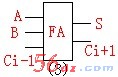

(2)全加器的設計(它的邏輯符號為圖(3)所示)

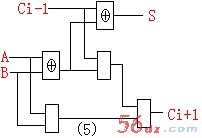

由于全加器考慮低位向高位的進位,所以它有三個輸入端和兩個輸出端。

設輸入變量為(加數)A、B、 Ci-1,輸出變量為 S、 Ci+1

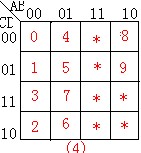

它的真值表為:如圖(4)所示

函數的邏輯表達式為:S=ABCi-1+ABCi-1+ABCi-1+ABCi-1=A![]() B

B![]() Ci-1

Ci-1

Ci+1=ABCi-1+ABCi-1+ABCi-1+ABCi-1 =(A![]() B)Ci-1+AB

B)Ci-1+AB

邏輯電路圖(用異或和與門構成)為:如圖(5)所示

(3)全加器的應用

因為加法器是數字系統中最基本的邏輯器件,所以它的應用很廣。它可用于二進制的減法運算、乘法運算,BCD碼的加、減法,碼組變換,數碼比較等。

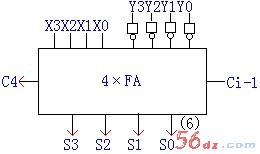

例 1:用全加器構成二進制減法器。

以四位二進制為例。(減法可轉換為加補運算)

設兩組四位二進制分別為X3X2X1X0和Y3Y2Y1Y0,把Y3Y2Y1Y0先進行求補然后再進行加法運算。

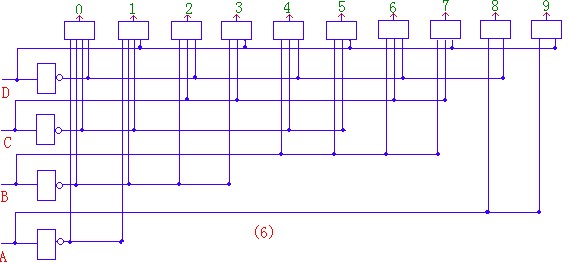

因為求補是逐位求反后再加“1”所以它的邏輯電路圖為如圖(6)所示:

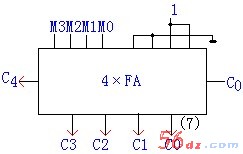

例 2:采用四位全加器完成8421BCD碼轉換為余3代碼。

由于8421BCD碼加0011即為余3代碼,因此轉換電路就是加法電路。

設8421BCD碼四位又高位到低位為M3、M2、M1、M0,余3代碼的四位由高到低為C3、C2、C1、C0 。

它的邏輯電路圖為如圖(7)所示:

二:編碼器和譯碼器

指定二進制代碼代表特定的信號的過程就叫編碼。把某一組二進制代碼的特定含義譯出的過程叫譯碼。

(1)編碼器 因為n位二進制數碼有2n種狀態,所以它可代表2n組信息。我們在編碼過程中一般是采用編碼矩陣和編碼表,編碼矩陣就是在卡諾圖上指定每一方格代表某一自然數,把這些自然數填入相應的方格。

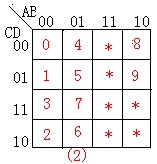

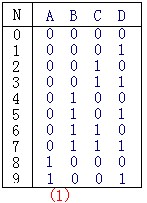

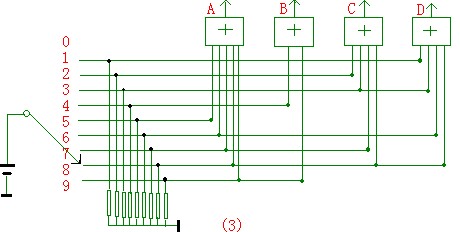

例 1:把0、1、2、...、9編為5421BCD碼.

先來確定編碼表如圖(1)所示和編碼矩陣如圖(2)所示:

由編碼表確定各輸出端的邏輯表達式是:

A=5+6+7+8+9

B=4+9

C=2+3+7+8

D=1+3+6+8

根據這些表達式可用或門組成

邏輯電路如圖(3)所示:

(2):譯碼器 編碼的逆過程就是譯碼。

譯碼就是把代碼譯為一定的輸出信號,以表示它的原意。實現譯碼的電路就是譯碼器。

譯碼器可分為二進制譯碼器、十進制譯碼器、集成譯碼器和數字顯示譯碼驅動電路。其中二進制譯碼器是一種最簡單的變量譯碼器,它的輸出端全是最小項。

例 2:設計一譯碼電路把8421BCD碼的0、1、2、...、9譯出來.

四位二進制有十六種狀態,而實際只需要十種,因此其余項作無關項考慮.

其編碼矩陣為如圖(4)所示.

我們通過編碼矩陣可得如下譯碼關系:如圖(5)所示.

所以它的邏輯電路圖為(用與門和與非門實現)

如圖(6)所示:

集成譯碼器的工作原理與其它譯碼器一樣,但它有它的特點.

它的特點為:

輸入采用緩沖級;(減輕信號負載)

輸出為反碼;低電平有效(減輕輸出功率)

增加了使能端.(便于擴展功能)

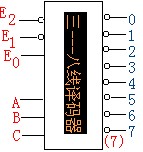

目前常用的典型的集成譯碼器是三------八譯碼器。

它的邏輯符號為.如圖(7)所示: 注:其中E0E1E2為使能端,只有當E1、E2為0時E0為1時此譯碼器才工作。

三:數據選擇器和多路分配器

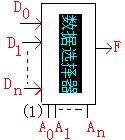

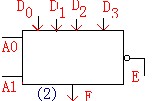

(1)數據選擇器 它就是從多個輸入端中選擇一路輸出,它相當于一個多路開關它的邏輯符號如圖(1)所示:其中D0D1、、、Dn是數據輸入端;A0A1、、、An為地址變量(有n個地址變量就有2n個輸入端).

(1)數據選擇器 它就是從多個輸入端中選擇一路輸出,它相當于一個多路開關它的邏輯符號如圖(1)所示:其中D0D1、、、Dn是數據輸入端;A0A1、、、An為地址變量(有n個地址變量就有2n個輸入端).

常用的有二選一,四選一,八選一和十六選一,若需更多則由上述擴展。

例 3:如圖(2)所示的四選一數據選擇器,試寫出它的輸出邏輯表達式和功能表

它的邏輯輸出表達式為 F=(A0A1D0+A0A1D1+A0A1D2+A0A1D3)E

它的功能表為:如下表所示

從表上我們可以看出當使能端E為“1”時輸出為“0”即禁止,只有當使能端為“0”時選擇器才有效。

例 4:把四選一擴展為八選一。

地址

使能端

輸入

輸出

A0

A1

E

D

F

* *

1

*

0

0 0

0

D0---D3

D0

0 1

0

D0---D3

D1

1 0

0

D0---D3

D2

1 1

0

D0---D3

D3

八選一要有八個輸入變量,因此需要三個地址變量(我們把其中一個A0作為使能段);

四選一只能有四個輸入變量,所以我們需要兩個四選一和一個非門.非門的作用是改變使能端的電平,減少使能端.先列出它的功能表如下表所示:

邏輯電路圖如圖(3)所示:

(2)多路分配器 它的功能是把輸入數據分配給不同的通道上,相當于一個單刀多擲開關。

A0

A1

A2

D

F

0 0 0

D0----D7

D0

0 0 1

D0----D7

D1

0 1 0

D0----D7

D2

0 1 1

D0----D7

D3

1 0 0

D0----D7

D4

1 0 1

D0----D7

D5

1 1 0

D0----D7

D6

1 1 1

D0----D7

D7

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底