ĪĪĪĪę╗Īó╝»│╔ķTļŖ┬Ę

ĪĪĪĪöĄ(sh©┤)ūų╝»│╔ļŖ┬Ę░┤Ųõā╚(n©©i)▓┐ėąį┤Ų„╝■Ą─▓╗═¼┐╔ęįĘų×ķā╔┤¾ŅÉŻ║ę╗ŅÉ×ķļpśOą═Š¦¾w╣▄╝»│╔ļŖ┬ĘŻ©TTLļŖ┬ĘŻ®Ż╗┴Ēę╗ŅÉ×ķå╬śOą═╝»│╔ļŖ┬ĘŻ©MOS╣▄ĮM│╔Ą─ļŖ┬ĘŻ®ĪŻ

ĪĪĪĪ1Ż«TTL╝»│╔▀ē▌ŗķTļŖ┬Ę

ĪĪĪĪŻ©1Ż®TTL┼cĘŪķT

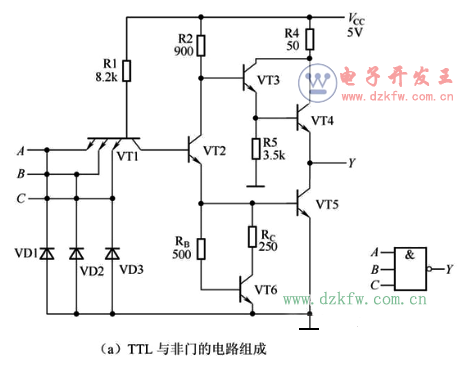

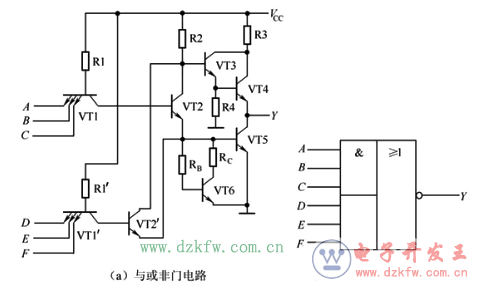

ĪĪĪĪCT74Sąż╠ž╗∙ŽĄ┴ąTTL┼cĘŪķTĄ─ļŖ┬ĘĮM│╔╚ńłD2-19Ż©aŻ®╦∙╩ŠŻ¼╦³ė╔▌ö╚ļ╝ēĪóųąķg╝ēĪó▌ö│÷╝ē3éĆ▓┐ĘųĮM│╔ĪŻ

ĪĪĪĪ

ĪĪĪĪłD2-19 TTL┼cĘŪķTļŖ┬ĘłD

ĪĪĪĪ▌ö╚ļ╝ēŻ║ė╔ČÓ░l(f©Ī)╔õśO╣▄VT1║═ļŖūĶR1ĮM│╔Ż¼ČÓ░l(f©Ī)╔õśO╣▄Ą─3éĆ░l(f©Ī)╔õĮY(ji©”)×ķ3éĆPNĮY(ji©”)ĪŻŲõū„ė├╩Ūī”▌ö╚ļūā┴┐AĪóBĪóCīŹ¼F(xi©żn)▀ē▌ŗ┼cŻ¼╦∙ęį╦³ŽÓ«öė┌ę╗éĆ┼cķTĪŻ

ĪĪĪĪųąķg╝ēŻ║ė╔VT2ĪóR2║═VT6ĪóRBĪóRCĮM│╔Ż¼VT2╝»ļŖśO║═░l(f©Ī)╔õśO═¼Ģr▌ö│÷ā╔éĆ▀ē▌ŗļŖŲĮŽÓĘ┤Ą─ą┼╠¢Ż¼ė├ęį“ī(q©▒)äėVT3║═VT5ĪŻ

ĪĪĪĪ▌ö│÷╝ēŻ║ė╔VT3ĪóVT4ĪóVT5║═R4ĪóR5ĮM│╔Ż¼╦³▓╔ė├┴╦▀_┴ųŅDĮY(ji©”)śŗ(g©░u)Ż¼VT3║═VT4ĮM│╔Å═║Ž╣▄ĮĄĄ═┴╦▌ö│÷Ė▀ļŖŲĮĢrĄ─▌ö│÷ļŖūĶŻ¼╠ßĖ▀┴╦Ħžō▌d─▄┴”ĪŻ

ĪĪĪĪTTL ┼cĘŪķTĄ─▀ē▌ŗĘ¹╠¢╚ńłD 2-19Ż©bŻ®╦∙╩ŠŻ╗▀ē▌ŗ▒Ē▀_╩Į×ķŻ║

ĪĪĪĪī”łD2-19╦∙╩ŠļŖ┬ĘŻ¼╚ń╣¹Ė▀ļŖŲĮė├1▒Ē╩ŠŻ¼Ą═ļŖŲĮė├0▒Ē╩ŠŻ¼ät┐╔┴ą│÷łD2-19╦∙╩ŠĄ─šµųĄ▒ĒŻ¼╚ń▒Ē2-1╦∙╩ŠĪŻ

ĪĪĪĪ

ĪĪĪĪ▒Ē2-1 TTL┼cĘŪķTšµųĄ▒Ē

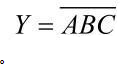

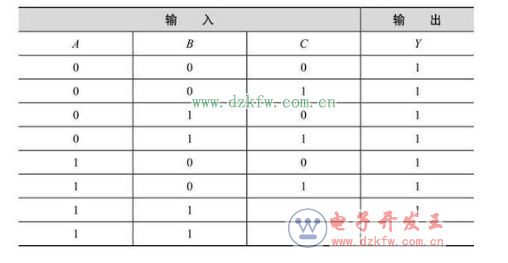

ĪĪĪĪŻ©2Ż®╝»ļŖśOķ_┬Ę┼cĘŪķTŻ©OCķTŻ®

ĪĪĪĪó┘ ╣żū„įŁ└ĒĪŻ

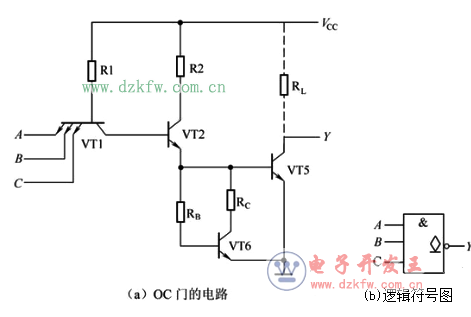

ĪĪĪĪ╝»ļŖśOķ_┬Ę┼cĘŪķTę▓Įą OC ķTŻ¼─▄╩╣ķTļŖ┬Ę▌ö│÷Ą─ļŖē║Ė▀ė┌ļŖ┬ĘĄ─Ė▀ļŖŲĮļŖē║ųĄŻ¼ŪęķTļŖ┬ĘĄ─▌ö│÷Č╦┐╔ęį▓ó┬ō(li©ón)ęįīŹ¼F(xi©żn)▀ē▌ŗ┼c╣”─▄Ż¼╝┤ŠĆ┼cŻ©ę╗░ŃĄ─TTLķTļŖ┬Ę▓╗─▄ŠĆ┼cŻ®ĪŻ

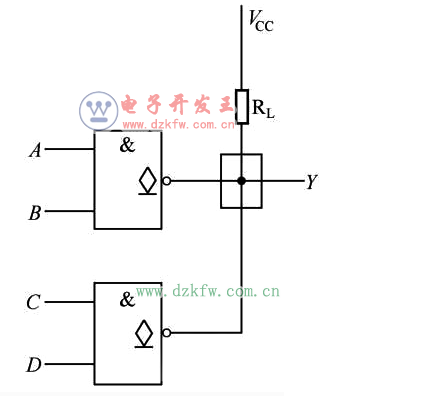

ĪĪĪĪOCķTĄ─ļŖ┬Ę╚ńłD2-20Ż©aŻ®╦∙╩ŠŻ¼▀ē▌ŗĘ¹╠¢╚ńłD2-20Ż©bŻ®╦∙╩ŠŻ¼▀ē▌ŗ▒Ē▀_╩Į×ķŻ║

ĪĪĪĪ

ĪĪĪĪłD2-20 ╝»ļŖśOķ_┬Ę┼cĘŪķT╝░▀ē▌ŗĘ¹╠¢

ĪĪĪĪó┌ OC ķTĄ─æ¬ė├ĪŻ

ĪĪĪĪOCķT┐╔ęįīŹ¼F(xi©żn)ŠĆ┼cŻ¼╚ńłD2-21╦∙╩ŠŻ¼▀ē▌ŗ▒Ē▀_╩Į×ķ![]() Ż╗“ī(q©▒)äė’@╩ŠŲ„ĪóīŹ¼F(xi©żn)ļŖŲĮ▐D(zhu©Żn)ōQŻ¼╚ńłD2-22╦∙╩ŠĪŻ

Ż╗“ī(q©▒)äė’@╩ŠŲ„ĪóīŹ¼F(xi©żn)ļŖŲĮ▐D(zhu©Żn)ōQŻ¼╚ńłD2-22╦∙╩ŠĪŻ

ĪĪĪĪ

ĪĪĪĪłD2-21 ė├OCķTīŹ¼F(xi©żn)ŠĆ┼c

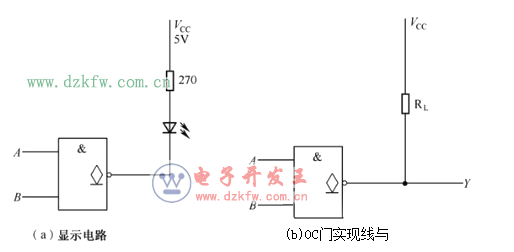

ĪĪĪĪŻ©3Ż®┼c╗“ĘŪķT

ĪĪĪĪ┼c╗“ĘŪķTļŖ┬Ę╚ńłD2-23Ż©aŻ®╦∙╩ŠŻ¼▀ē▌ŗĘ¹╠¢╚ńłD2-23Ż©bŻ®╦∙╩ŠŻ¼▀ē▌ŗ▒Ē▀_╩Į×ķŻ║

ĪĪĪĪ

ĪĪĪĪłD2-22 “ī(q©▒)äė’@╩ŠŲ„ĪóīŹ¼F(xi©żn)ļŖŲĮ▐D(zhu©Żn)ōQ

ĪĪĪĪ

ĪĪĪĪłD2-23 ┼c╗“ĘŪķT╝░▀ē▌ŗĘ¹╠¢

ĪĪĪĪŻ©4Ż®╚²æB(t©żi)▌ö│÷ķT

ĪĪĪĪ╚²æB(t©żi)▌ö│÷ķT╩ŪųĖ▓╗āH┐╔▌ö│÷Ė▀ļŖŲĮĪóĄ═ļŖŲĮā╔éĆĀŅæB(t©żi)Ż¼Č°Ūę▀Ć┐╔▌ö│÷Ė▀ūĶĀŅæB(t©żi)Ą─ķTļŖ┬ĘŻ¼╚ńłD2-24╦∙╩ŠŻ¼![]() ×ķ┐žųŲČ╦ĪŻ

×ķ┐žųŲČ╦ĪŻ

ĪĪĪĪ«ö![]() =0ĢrŻ¼G▌ö│÷P=1Ż¼VDĮžų╣Ż¼▌ö│÷Y=

=0ĢrŻ¼G▌ö│÷P=1Ż¼VDĮžų╣Ż¼▌ö│÷Y=![]() Ż¼╚²æB(t©żi)ķT╠Äė┌╣żū„ĀŅæB(t©żi)ĪŻ

Ż¼╚²æB(t©żi)ķT╠Äė┌╣żū„ĀŅæB(t©żi)ĪŻ![]() Ą═ļŖŲĮėąą¦ĪŻ

Ą═ļŖŲĮėąą¦ĪŻ

ĪĪĪĪ

ĪĪĪĪłD2-24 ╚²æB(t©żi)▌ö│÷┼cĘŪķT╝░Ųõ▀ē▌ŗĘ¹╠¢

ĪĪĪĪ«ö![]() =1ĢrŻ¼G▌ö│÷P=0Ż¼VDī¦═©Ż¼▌ö│÷Ė▀ūĶĀŅæB(t©żi)ĪŻ

=1ĢrŻ¼G▌ö│÷P=0Ż¼VDī¦═©Ż¼▌ö│÷Ė▀ūĶĀŅæB(t©żi)ĪŻ

ĪĪĪĪ2Ż«CMOS╝»│╔▀ē▌ŗķT

ĪĪĪĪ║═ TTL öĄ(sh©┤)ūų╝»│╔ļŖ┬ĘŽÓ▒╚Ż¼CMOS ļŖ┬ĘĄ─═╗│÷╠ž³c╩Ū╬ó╣”║─ĪóĖ▀┐╣Ė╔ö_─▄┴”ĪŻ

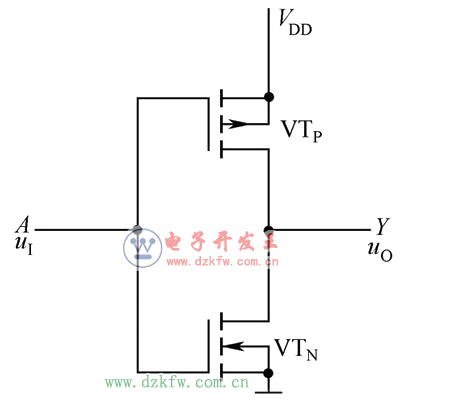

ĪĪĪĪŻ©1Ż®CMOSĘ┤ŽÓŲ„

ĪĪĪĪė╔ā╔éĆł÷ą¦æ¬╣▄ĮM│╔╗źča╣żū„ĀŅæB(t©żi)Ż¼╚ńłD 2-25 ╦∙╩ŠĪŻ▀ē▌ŗ▒Ē▀_╩Į×ķŻ║

ĪĪĪĪ

ĪĪĪĪłD2-25 CMOS Ę┤ŽÓŲ„

ĪĪĪĪŻ©2Ż®CMOS┼cĘŪķT

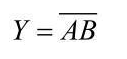

ĪĪĪĪ╚ńłD2-26╦∙╩ŠŻ¼ā╔éĆ┤«┬ō(li©ón)Ą─į÷ÅŖą═NMOS╣▄VTN1║═VTN2×ķ“ī(q©▒)äė╣▄Ż¼ā╔éĆ▓ó┬ō(li©ón)Ą─į÷ÅŖą═PMOS╣▄VTP1║═VTP2×ķžō▌d╣▄Ż¼ĮM│╔CMOS┼cĘŪķTŻ¼▀ē▌ŗ▒Ē▀_╩Į×ķŻ║ ĪŻ

ĪŻ

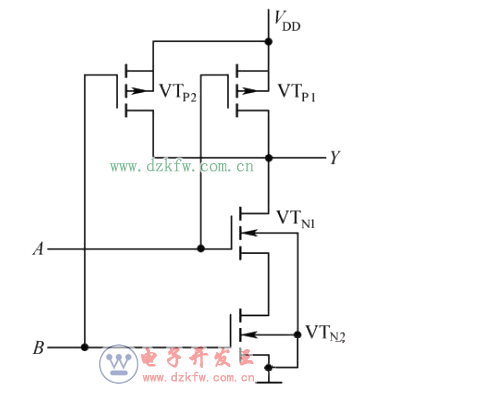

ĪĪĪĪŻ©3Ż®CMOS╗“ĘŪķT

ĪĪĪĪ╚ńłD2-27╦∙╩ŠŻ¼ā╔éĆ▓ó┬ō(li©ón)Ą─į÷ÅŖą═NMOS╣▄VTN1║═VTN2×ķ“ī(q©▒)äė╣▄Ż¼ā╔éĆ┤«┬ō(li©ón)Ą─į÷ÅŖą═PMOS╣▄VTP1║═VTP2×ķžō▌d╣▄Ż¼ĮM│╔CMOS╗“ĘŪķTŻ¼▀ē▌ŗ▒Ē▀_╩Į×ķŻ║

ĪĪĪĪ

ĪĪĪĪłD2-26 CMOS ┼cĘŪķT

ĪĪĪĪ

ĪĪĪĪłD2-27 CMOS ╗“ĘŪķT

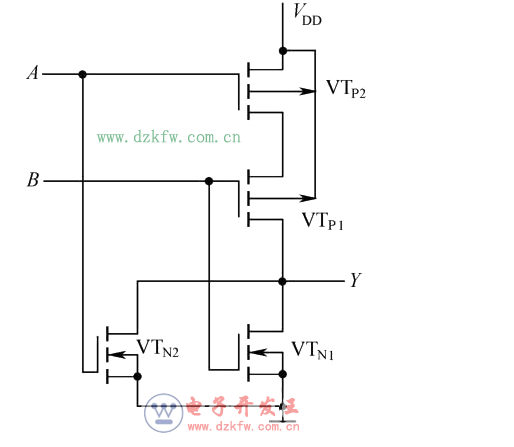

ĪĪĪĪŻ©4Ż®CMOSé„▌öķT

ĪĪĪĪīóā╔éĆģóöĄ(sh©┤)ī”ĘQę╗ų┬Ą─į÷ÅŖą═NMOS╣▄VTN║═PMOS╣▄VTP▓ó┬ō(li©ón)┐╔śŗ(g©░u)│╔CMOSé„▌öķTŻ¼ļŖ┬Ę║═▀ē▌ŗĘ¹╠¢╚ńłD2-28╦∙╩ŠĪŻ

ĪĪĪĪ

ĪĪĪĪłD2-28 CMOS é„▌öķT╝░▀ē▌ŗĘ¹╠¢

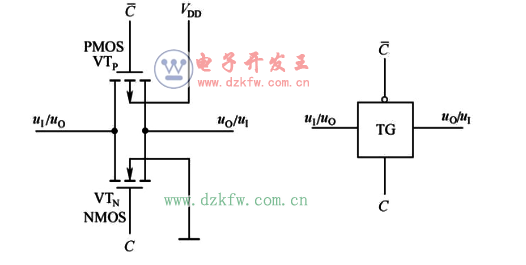

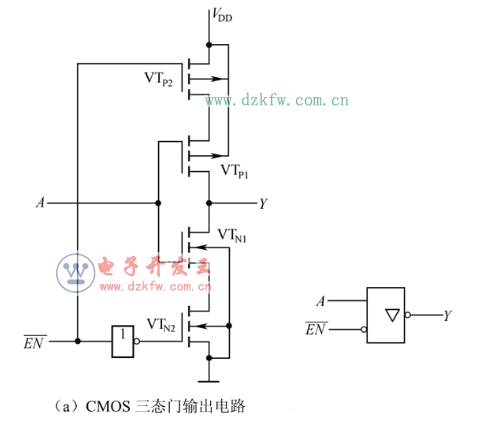

ĪĪĪĪŻ©5Ż®CMOS╚²æB(t©żi)ķT

ĪĪĪĪłD 2-29Ż©aŻ®╦∙╩Š×ķĄ═ļŖŲĮ┐žųŲĄ─╚²æB(t©żi)ķT▌ö│÷Ż¼łD 2-29Ż©bŻ®×ķ▀ē▌ŗĘ¹╠¢ĪŻ

ĪĪĪĪ

ĪĪĪĪłD2-29 CMOS ╚²æB(t©żi)ķT▌ö│÷╝░▀ē▌ŗĘ¹╠¢

ĪĪĪĪ«ö![]() ĢrŻ¼VTP2║═VTN2ī¦═©Ż¼VTN1║═VTP1ĮM│╔Ą─CMOSĘ┤ŽÓŲ„╣żū„Ż¼╦∙ęį

ĢrŻ¼VTP2║═VTN2ī¦═©Ż¼VTN1║═VTP1ĮM│╔Ą─CMOSĘ┤ŽÓŲ„╣żū„Ż¼╦∙ęį ĪŻ

ĪŻ

ĪĪĪĪ«ö![]() Ż¼VTP2║═VTN2═¼ĢrĮžų╣Ż¼▌ö│÷Yī”Ąž║═ī”ļŖį┤VDDČ╝│╩Ė▀ūĶĀŅæB(t©żi)ĪŻ

Ż¼VTP2║═VTN2═¼ĢrĮžų╣Ż¼▌ö│÷Yī”Ąž║═ī”ļŖį┤VDDČ╝│╩Ė▀ūĶĀŅæB(t©żi)ĪŻ

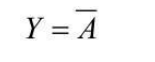

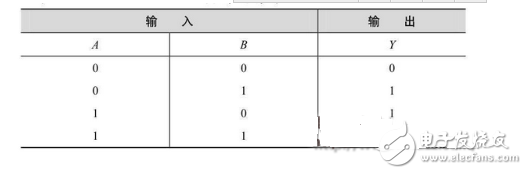

ĪĪĪĪŻ©6Ż®CMOS«É╗“ķT

ĪĪĪĪłD2-30Ż©aŻ®╦∙╩Š×ķ«É╗“ķTŻ¼łD2-30Ż©bŻ®×ķ▀ē▌ŗĘ¹╠¢ĪŻ

ĪĪĪĪ

ĪĪĪĪłD2-30 CMOS «É╗“ķT╝░▀ē▌ŗĘ¹╠¢

ĪĪĪĪ«ö▌ö╚ļA=B=0╗“A=B=1ĢrŻ¼╝┤▌ö╚ļą┼╠¢ŽÓ═¼Ż¼▌ö│÷Y=0Ż╗«ö▌ö╚ļA=1╗“B=1ĢrŻ¼╝┤▌ö╚ļą┼╠¢▓╗═¼Ż¼▌ö│÷Y=1ĪŻŲõšµųĄ▒Ē╚ń▒Ē2-2╦∙╩ŠĪŻ

ĪĪĪĪ

ĪĪĪĪ▒Ē2-2 «É╗“ķTšµųĄ▒Ē

ĪĪĪĪ3Ż«Å═║ŽķTļŖ┬Ę

ĪĪĪĪ│²┴╦╔Ž╩÷ĮķĮBĄ─▀ē▌ŗķTļŖ┬Ę═ŌŻ¼▀Ćėą╗“ĘŪķTĪó«É╗“ķTĪó═¼╗“ķTĄ╚Ż¼▒Ē2-3╩Ū╗∙▒ŠķT║═│Żė├Å═║ŽķTĄ─▀ē▌ŗĘ¹╠¢Īó▀ē▌ŗ▒Ē▀_╩Į╝░▀ē▌ŗ╣”─▄ĪŻ

ĪĪĪĪ▒Ē2-3 ╗∙▒ŠķT║═│Żė├Å═║ŽķTĄ─ī”šš▒Ē

ĪĪĪĪČ■ĪóĮM║Ž▀ē▌ŗļŖ┬Ę

ĪĪĪĪ▀ē▌ŗļŖ┬Ęį┌╚╬║╬Ģr┐╠Ą─▌ö│÷ĀŅæB(t©żi)ų╗╚ĪøQė┌▀@ę╗Ģr┐╠Ą─▌ö╚ļĀŅæB(t©żi)Ż¼Č°┼cļŖ┬ĘĄ─įŁüĒĀŅæB(t©żi)¤oĻP(gu©Īn)Ż¼ätįōļŖ┬ĘĘQ×ķĮM║Ž▀ē▌ŗļŖ┬ĘĪŻ

ĪĪĪĪ1Ż«ĮM║Ž▀ē▌ŗļŖ┬ĘĄ─Ęų╬÷ĘĮĘ©

ĪĪĪĪŻ©1Ż®Ęų╬÷▓Į¾E

ĪĪĪĪó┘ Ė∙ō■(j©┤)ĮoČ©Ą─▀ē▌ŗļŖ┬Ęīæ│÷▌ö│÷▀ē▌ŗĻP(gu©Īn)ŽĄ╩ĮĪŻę╗░ŃÅ─▌ö╚ļČ╦Ž“▌ö│÷Č╦ų╝ēīæ│÷Ė„éĆķT▌ö│÷ī”Ųõ▌ö╚ļĄ─▀ē▌ŗ▒Ē▀_╩ĮŻ¼Å─Č°īæ│÷š¹éĆ▀ē▌ŗļŖ┬ĘĄ─▌ö│÷ī”▌ö╚ļūā┴┐Ą─▀ē▌ŗ║»öĄ(sh©┤)╩ĮĪŻ▒žę¬ĢrŻ¼┐╔▀Mąą╗»║åŻ¼Ū¾│÷▌ö│÷▀ē▌ŗ║»öĄ(sh©┤)╩ĮĪŻ

ĪĪĪĪó┌ ┴ą│÷▀ē▌ŗ║»öĄ(sh©┤)Ą─šµųĄ▒ĒĪŻīó▌ö╚ļūā┴┐Ą─ĀŅæB(t©żi)ęįūį╚╗Č■▀MųŲöĄ(sh©┤)Ēśą“Ą─Ė„ĘN╚ĪųĄĮM║Ž┤·╚ļ▌ö│÷▀ē▌ŗ║»öĄ(sh©┤)╩ĮŻ¼Ū¾│÷ŽÓæ¬Ą─▌ö│÷ĀŅæB(t©żi)Ż¼▓ó╠Ņ╚ļ▒ĒųąŻ¼╝┤Ą├šµųĄ▒ĒĪŻ

ĪĪĪĪó█ Ė∙ō■(j©┤)šµųĄ▒Ē║═▀ē▌ŗ▒Ē▀_╩Įī”▀ē▌ŗļŖ┬Ę▀MąąĘų╬÷Ż¼ūŅ║¾┤_Č©Ųõ╣”─▄ĪŻ

ĪĪĪĪŻ©2Ż®Ęų╬÷┼e└²

ĪĪĪĪĘų╬÷łD2-31╦∙╩Š▀ē▌ŗļŖ┬ĘĄ─╣”─▄ĪŻ

ĪĪĪĪ

ĪĪĪĪłD2-31 ▀ē▌ŗļŖ┬Ę

ĪĪĪĪó┘ īæ│÷▌ö│÷▀ē▌ŗ║»öĄ(sh©┤)▒Ē▀_╩ĮŻ║

ĪĪĪĪ

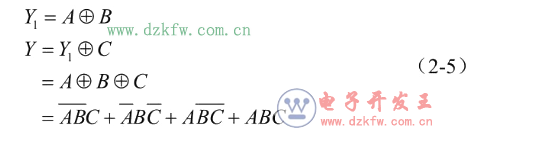

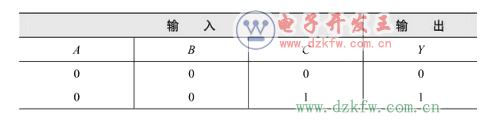

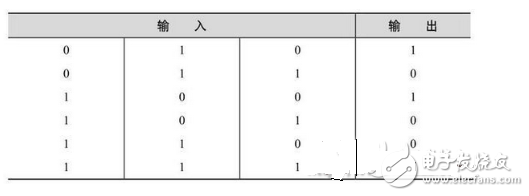

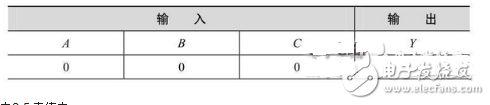

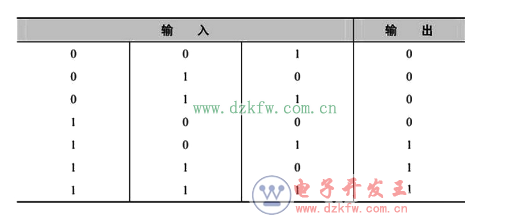

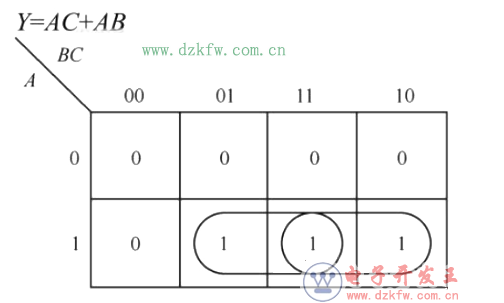

ĪĪĪĪó┌ ┴ą│÷▀ē▌ŗ║»öĄ(sh©┤)Ą─šµųĄ▒ĒĪŻīó▌ö╚ļAĪóBĪóC╚ĪųĄĄ─Ė„ĘNĮM║Ž┤·╚ļ╩ĮŻ©2-5Ż®ųąŻ¼Ū¾│÷▌ö│÷YĄ─ųĄĪŻė╔┤╦┴ą│÷šµųĄ▒ĒŻ¼ęŖ▒Ē2-4ĪŻ

ĪĪĪĪ

ĪĪĪĪ▒Ē2-4 šµųĄ▒Ē

ĪĪĪĪ

ĪĪĪĪ└m(x©┤)▒Ē

ĪĪĪĪó█ ▀ē▌ŗ╣”─▄Ęų╬÷ĪŻė╔▒Ē2-4┐╔ų¬Ż║į┌▌ö╚ļAĪóBĪóC▀@3éĆūā┴┐ųąŻ¼ėąŲµöĄ(sh©┤)éĆ1ĢrŻ¼▌ö│÷Y×ķ1Ż¼Ę±ätY×ķ0Ż¼ė╔┤╦┐╔ų¬Ż¼łD2-34×ķ▀@3╬╗ŲµąŻ“×ļŖ┬ĘĪŻ

ĪĪĪĪ2Ż«ĮM║Ž▀ē▌ŗļŖ┬ĘĄ─įO(sh©©)ėŗĘĮĘ©

ĪĪĪĪŻ©1Ż®įO(sh©©)ėŗ▓Į¾E

ĪĪĪĪĮM║Ž▀ē▌ŗļŖ┬ĘĄ─įO(sh©©)ėŗŻ¼æ¬ęįļŖ┬Ę║åå╬Īó╦∙ė├Ų„╝■ūŅ╔┘×ķ─┐ś╦Ż¼ŲõįO(sh©©)ėŗ▓Į¾E×ķŻ║

ĪĪĪĪó┘ Ęų╬÷įO(sh©©)ėŗę¬Ū¾Ż¼┴ą│÷šµųĄ▒ĒŻ╗

ĪĪĪĪó┌ Ė∙ō■(j©┤)šµųĄ▒Ēīæ│÷▌ö│÷▀ē▌ŗ║»öĄ(sh©┤)▒Ē▀_╩ĮŻ╗

ĪĪĪĪó█ ī”▌ö│÷▀ē▌ŗ║»öĄ(sh©┤)▀Mąą╗»║åŻ╗

ĪĪĪĪó▄ Ė∙ō■(j©┤)ūŅ║å▌ö│÷▀ē▌ŗ║»öĄ(sh©┤)╩Į«ŗ▀ē▌ŗłDĪŻ

ĪĪĪĪŻ©2Ż®įO(sh©©)ėŗ┼e└²

ĪĪĪĪįO(sh©©)ėŗę╗éĆAĪóBĪóC3éĆ╚╦▒ĒøQļŖ┬ĘĪŻ«ö▒ĒøQ─│éĆ╠ß░ĖĢrŻ¼ČÓöĄ(sh©┤)╚╦═¼ęŌŻ¼╠ß░Ė═©▀^Ż¼═¼ĢrAŠ▀ėąĘ±øQÖÓ(qu©ón)ĪŻė├┼cĘŪķTīŹ¼F(xi©żn)ĪŻ

ĪĪĪĪó┘ Ęų╬÷įO(sh©©)ėŗę¬Ū¾Ż¼┴ą│÷šµųĄ▒ĒŻ¼ęŖ▒Ē2-5ĪŻįO(sh©©)AĪóBĪóC═¼ęŌ╠ß░Ėė├1▒Ē╩ŠŻ¼▓╗═¼ęŌė├0▒Ē╩ŠŻ¼Y×ķ▒ĒøQĮY(ji©”)╣¹Ż¼╠ß░Ė═©▀^×ķ1Ż¼═©▓╗▀^×ķ0ĪŻ

ĪĪĪĪ

ĪĪĪĪ▒Ē2-5 šµųĄ▒Ē

ĪĪĪĪ

ĪĪĪĪ└m(x©┤)▒Ē

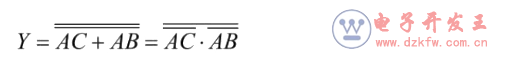

ĪĪĪĪó┌ īó▌ö│÷▀ē▌ŗ║»öĄ(sh©┤)╗»║åŻ¼ūāōQ×ķ┼cĘŪ▒Ē▀_╩ĮĪŻė╔łD 2-32 Ą─┐©ųZłD▀Mąą╗»║åŻ¼┐╔Ą├

ĪĪĪĪ

ĪĪĪĪłD2-32 ┐©ųZłD

ĪĪĪĪīó╔Ž╩Įūā╗»×ķ┼cĘŪ▒Ē▀_╩Į

ĪĪĪĪ

ĪĪĪĪó█ Ė∙ō■(j©┤)▌ö│÷▀ē▌ŗ║»öĄ(sh©┤)╩ĮŻ©2-6Ż®«ŗ▀ē▌ŗłDŻ¼╚ńłD2-33╦∙╩ŠĪŻ

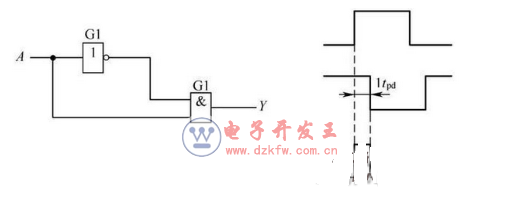

ĪĪĪĪ3Ż«ĮM║Ž▀ē▌ŗļŖ┬ĘųąĄ─ĖéĀÄ├░ļU

ĪĪĪĪŻ©1Ż®ĖéĀÄ├░ļU¼F(xi©żn)Ž¾╝░Ųõ«a(ch©Żn)╔·Ą─įŁę“

ĪĪĪĪą┼╠¢═©▀^ī¦ŠĆ║═ķTļŖ┬ĘĢrŻ¼Č╝┤µį┌ĢrķgĄ─čė▀tŻ¼ą┼╠¢░l(f©Ī)╔·ūā╗»Ģrę▓ėąę╗Č©Ą─╔Ž╔²Ģrķg║═Ž┬ĮĄĢrķgĪŻę“┤╦Ż¼═¼ę╗éĆķTĄ─ę╗ĮM▌ö╚ļą┼╠¢Ż¼═©▀^▓╗═¼öĄ(sh©┤)─┐Ą─ķTŻ¼Įø(j©®ng)▀^▓╗═¼ķLČ╚ī¦ŠĆĄ─é„▌öŻ¼ĄĮ▀_ķT▌ö╚ļČ╦Ą─ĢrķgĢ■ėąŽ╚ėą║¾Ż¼▀@ĘN¼F(xi©żn)Ž¾ĘQ×ķĖéĀÄĪŻ

ĪĪĪĪ

ĪĪĪĪłD2-33 ▀ē▌ŗļŖ┬Ę

ĪĪĪĪ▀ē▌ŗķTę“▌ö╚ļČ╦Ą─ĖéĀÄČ°ī¦ų┬▌ö│÷«a(ch©Żn)╔·▓╗æ¬ėąĄ─╝ŌĘÕĖ╔ö_├}ø_Ż©ėųĘQ▀^Č╔Ė╔ö_├}ø_Ż®Ą─¼F(xi©żn)Ž¾Ż¼ĘQ×ķ├░ļUĪŻ╚ńłD2-34╦∙╩ŠĪŻ

ĪĪĪĪ

ĪĪĪĪłD2-34 «a(ch©Żn)╔·š²╝ŌĘÕĖ╔ö_├}ø_├░ļU

ĪĪĪĪŻ©2Ż®├░ļU¼F(xi©żn)Ž¾Ą─┼ąäe

ĪĪĪĪį┌ĮM║Ž▀ē▌ŗļŖ┬ĘųąŻ¼╩Ūʱ┤µį┌├░ļU¼F(xi©żn)Ž¾Ż¼┐╔═©▀^▀ē▌ŗ║»öĄ(sh©┤)üĒ┼ąäeĪŻ╚ń╣¹Ė∙ō■(j©┤)ĮM║Ž▀ē▌ŗļŖ┬Ęīæ│÷Ą─▌ö│÷▀ē▌ŗ║»öĄ(sh©┤)į┌ę╗Č©Śl╝■Ž┬┐╔║å╗»│╔Ž┬┴ąā╔ĘNą╬╩ĮĢrŻ¼ätįōĮM║Ž▀ē▌ŗļŖ┬Ę┤µį┌├░ļU¼F(xi©żn)Ž¾Ż¼╝┤Ż║

ĪĪĪĪ

ĪĪĪĪ└²╚ńŻ¼║»öĄ(sh©┤)╩Į Ż¼į┌A=C=0ĢrŻ¼

Ż¼į┌A=C=0ĢrŻ¼ ĪŻ╚¶ų▒ĮėĖ∙ō■(j©┤)▀@éĆ▀ē▌ŗ▒Ē▀_╩ĮĮM│╔▀ē▌ŗļŖ┬ĘŻ¼ät┐╔─▄│÷¼F(xi©żn)ĖéĀÄ├░ļUĪŻ

ĪŻ╚¶ų▒ĮėĖ∙ō■(j©┤)▀@éĆ▀ē▌ŗ▒Ē▀_╩ĮĮM│╔▀ē▌ŗļŖ┬ĘŻ¼ät┐╔─▄│÷¼F(xi©żn)ĖéĀÄ├░ļUĪŻ

ĪĪĪĪŻ©3Ż®Ž¹│²├░ļU¼F(xi©żn)Ž¾Ą─ĘĮĘ©

ĪĪĪĪó┘į÷╝ėČÓėÓĒŚĪŻ└²╚ńŻ║ Ż¼«öA=1Ż¼C=1ĢrŻ¼┤µį┌ų°ĖéĀÄ├░ļUĪŻĖ∙ō■(j©┤)▀ē▌ŗ┤·öĄ(sh©┤)Ą─╗∙▒Š╣½╩ĮŻ¼į÷╝ėę╗ĒŚ ACŻ¼║»öĄ(sh©┤)╩Į▓╗ūāŻ¼ģsŽ¹│²┴╦ĖéĀÄ├░ļUŻ¼╝┤

Ż¼«öA=1Ż¼C=1ĢrŻ¼┤µį┌ų°ĖéĀÄ├░ļUĪŻĖ∙ō■(j©┤)▀ē▌ŗ┤·öĄ(sh©┤)Ą─╗∙▒Š╣½╩ĮŻ¼į÷╝ėę╗ĒŚ ACŻ¼║»öĄ(sh©┤)╩Į▓╗ūāŻ¼ģsŽ¹│²┴╦ĖéĀÄ├░ļUŻ¼╝┤ ĪŻ

ĪŻ

ĪĪĪĪó┌ ╝ėĘŌµi├}ø_ĪŻį┌▌ö╚ļą┼╠¢«a(ch©Żn)╔·ĖéĀÄ├░ļUĢrķgā╚(n©©i)Ż¼ę²╚ļę╗éĆ├}ø_īó┐╔─▄«a(ch©Żn)╔·╝ŌĘÕĖ╔ö_├}ø_Ą─ķTĘŌµiūĪĪŻĘŌµi├}ø_æ¬į┌▌ö╚ļą┼╠¢▐D(zhu©Żn)ōQŪ░ĄĮüĒŻ¼▐D(zhu©Żn)ōQ║¾Ž¹╩¦ĪŻ

ĪĪĪĪó█ ╝ė▀x═©├}ø_ĪŻī”▌ö╚ļ┐╔─▄«a(ch©Żn)╔·╝ŌĘÕĖ╔ö_├}ø_Ą─ķTļŖ┬Ęį÷╝ėę╗éĆĮė▀x═©ą┼╠¢Ą─▌ö╚ļČ╦Ż¼ų╗ėąį┌▌ö╚ļą┼╠¢▐D(zhu©Żn)ōQ═Ļ│╔▓óĘĆ(w©¦n)Č©║¾Ż¼▓┼ę²╚ļ▀x═©├}ø_īó╦³┤“ķ_Ż¼┤╦Ģr▓┼į╩įSėą▌ö│÷ĪŻ

ĪĪĪĪó▄ Įė╚ļ×V▓©ļŖ╚▌ĪŻ╚ń╣¹▀ē▌ŗļŖ┬Ęį┌▌^┬²╦┘Č╚Ž┬╣żū„Ż¼┐╔ęįį┌▌ö│÷Č╦▓ó┬ō(li©ón)ę╗ļŖ╚▌Ų„ĪŻė╔ė┌╝ŌĘÕĖ╔ö_├}ø_Ą─īÆČ╚ę╗░ŃČ╝║▄šŁŻ¼ę“┤╦ė├ļŖ╚▌╝┤┐╔╬³╩šĄ¶╝ŌĘÕĖ╔ö_├}ø_ĪŻ

ĪĪĪĪó▌ ą▐Ė─▀ē▌ŗįO(sh©©)ėŗĪŻ

ĪĪĪĪ╚²ĪóĢrą“▀ē▌ŗļŖ┬Ę

ĪĪĪĪ┼cĮM║Ž▀ē▌ŗļŖ┬Ę▓╗═¼Ż¼Ģrą“▀ē▌ŗļŖ┬Ęį┌╚╬║╬ę╗éĆĢr┐╠Ą─▌ö│÷ĀŅæB(t©żi)▓╗āH╚ĪøQė┌«öĢrĄ─▌ö╚ļą┼╠¢Ż¼Č°Ūę▀Ć╚ĪøQė┌ļŖ┬ĘįŁüĒĄ─ĀŅæB(t©żi)ĪŻ

ĪĪĪĪ1Ż«═¼▓ĮĢrą“▀ē▌ŗļŖ┬ĘĄ─Ęų╬÷ĘĮĘ©

ĪĪĪĪŻ©1Ż®Ęų╬÷▓Į¾E

ĪĪĪĪó┘ īæĘĮ│╠╩ĮĪŻīæ│÷Ģrą“▀ē▌ŗļŖ┬ĘĄ─▌ö│÷▀ē▌ŗ▒Ē▀_╩ĮŻ©╝┤▌ö│÷ĘĮ│╠Ż®ĪóĖ„ė|░l(f©Ī)Ų„▌ö╚ļČ╦Ą─▀ē▌ŗ▒Ē▀_╩ĮŻ©╝┤“ī(q©▒)äėĘĮ│╠Ż®║═Ģrą“▀ē▌ŗļŖ┬ĘĄ─ĀŅæB(t©żi)ĘĮ│╠ĪŻ

ĪĪĪĪó┌ ┴ąĀŅæB(t©żi)▐D(zhu©Żn)ōQšµųĄ▒ĒĪŻīóļŖ┬Ę¼F(xi©żn)ĀŅĄ─Ė„ĘN╚ĪųĄ┤·╚ļĀŅæB(t©żi)ĘĮ│╠║═▌ö│÷ĘĮ│╠ųą▀Mąąėŗ╦ŃŻ¼Ū¾│÷ŽÓæ¬Ą─┤╬æB(t©żi)║═▌ö│÷Ż¼Å─Č°┴ą│÷ĀŅæB(t©żi)▐D(zhu©Żn)ōQšµųĄ▒ĒĪŻ

ĪĪĪĪó█ ▀ē▌ŗ╣”─▄Ą─šf├„ĪŻĖ∙ō■(j©┤)ĀŅæB(t©żi)▐D(zhu©Żn)ōQšµųĄ▒ĒüĒšf├„ļŖ┬ĘĄ─▀ē▌ŗ╣”─▄ĪŻ

ĪĪĪĪó▄ «ŗ│÷ĀŅæB(t©żi)łD║═Ģrą“łDĪŻ

ĪĪĪĪŻ©2Ż®Ęų╬÷┼e└²

ĪĪĪĪĘų╬÷łD 2-35 ╦∙╩ŠļŖ┬ĘĄ─▀ē▌ŗ╣”─▄Ż¼▓ó«ŗ│÷ĀŅæB(t©żi)▐D(zhu©Żn)ōQłD║═Ģrą“łDĪŻ

ĪĪĪĪ

ĪĪĪĪłD2-35 ┤²Ęų╬÷▀ē▌ŗļŖ┬ĘłD

ĪĪĪĪó┘ īæĘĮ│╠╩ĮŻ║

ĪĪĪĪ▌ö│÷ĘĮ│╠Ż║![]()

ĪĪĪĪ“ī(q©▒)äėĘĮ│╠Ż║

ĪĪĪĪĀŅæB(t©żi)ĘĮ│╠Ż║īó“ī(q©▒)äėĘĮ│╠╩Į┤·╚ļ JK ė|░l(f©Ī)Ų„Ą─╠žąįĘĮ│╠Qn+1=![]() Ż¼Ą├ĄĮļŖ┬ĘĄ─ĀŅæB(t©żi)ĘĮ│╠×ķ

Ż¼Ą├ĄĮļŖ┬ĘĄ─ĀŅæB(t©żi)ĘĮ│╠×ķ

ĪĪĪĪ

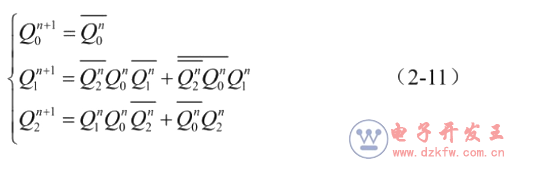

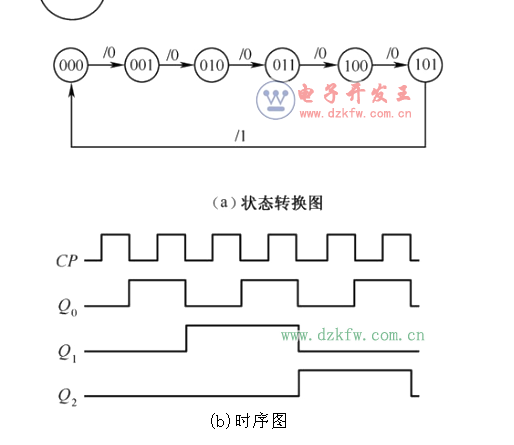

ĪĪĪĪó┌┴ąĀŅæB(t©żi)▐D(zhu©Żn)ōQšµųĄ▒ĒŻ║įōļŖ┬ĘĄ─¼F(xi©żn)ĀŅ×ķ![]() Ż¼┤·╚ļ▌ö│÷ĘĮ│╠Ż©2-9Ż®║═ĀŅæB(t©żi)ĘĮ│╠Ż©2-11Ż®ųą▀Mąąėŗ╦Ń║¾Ą├ Y=0 ║═

Ż¼┤·╚ļ▌ö│÷ĘĮ│╠Ż©2-9Ż®║═ĀŅæB(t©żi)ĘĮ│╠Ż©2-11Ż®ųą▀Mąąėŗ╦Ń║¾Ą├ Y=0 ║═![]() Ż¼╚╗║¾į┘īó001«öū„¼F(xi©żn)æB(t©żi)┤·╚ļĀŅæB(t©żi)ĘĮ│╠╩ĮŻ©2-11Ż®Ż¼Ą├

Ż¼╚╗║¾į┘īó001«öū„¼F(xi©żn)æB(t©żi)┤·╚ļĀŅæB(t©żi)ĘĮ│╠╩ĮŻ©2-11Ż®Ż¼Ą├![]() Ż¼ęį┤╦ŅÉ═ŲĪŻ┐╔Ū¾Ą├┐╔Ū¾Ą├▒Ē2-6╦∙╩ŠĄ─ĀŅæB(t©żi)▐D(zhu©Żn)ōQšµųĄ▒ĒĪŻ

Ż¼ęį┤╦ŅÉ═ŲĪŻ┐╔Ū¾Ą├┐╔Ū¾Ą├▒Ē2-6╦∙╩ŠĄ─ĀŅæB(t©żi)▐D(zhu©Żn)ōQšµųĄ▒ĒĪŻ

ĪĪĪĪ

ĪĪĪĪ▒Ē2-6 ĀŅæB(t©żi)▐D(zhu©Żn)ōQšµųĄ▒Ē

ĪĪĪĪó█ ▀ē▌ŗ╣”─▄šf├„Ż║ė╔▒Ē2-6┐╔┐┤│÷Ż¼łD2-35╦∙╩ŠļŖ┬Ęį┌▌ö╚ļĄ┌┴∙éĆėŗöĄ(sh©┤)├}ø_CPŻ¼ĘĄ╗žįŁüĒĄ─ĀŅæB(t©żi)Ż¼═¼Ģr▌ö│÷Č╦Y▌ö│÷ę╗éĆ▀M╬╗├}ø_ĪŻę“┤╦Ż¼įōļŖ┬Ę×ķ═¼▓Į┴∙▀MųŲėŗöĄ(sh©┤)Ų„ĪŻ

ĪĪĪĪ

ĪĪĪĪłD2-36 ĀŅæB(t©żi)▐D(zhu©Żn)ōQłD║═Ģrą“łD

ĪĪĪĪó▄ «ŗĀŅæB(t©żi)▐D(zhu©Żn)ōQłD║═Ģrą“łDĪŻĖ∙ō■(j©┤)▒Ē2-6┐╔«ŗ│÷łD2-36Ż©aŻ®╦∙╩ŠĄ─ĀŅæB(t©żi)▐D(zhu©Żn)ōQłDĪŻłDųąĄ─łA╚”ā╚(n©©i)▒Ē╩ŠļŖ┬Ęę╗éĆĀŅæB(t©żi)Ż¼╝²Ņ^▒Ē╩ŠĀŅæB(t©żi)▐D(zhu©Żn)ōQĘĮŽ“Ż¼╝²Ņ^ŠĆ╔ŽĘĮś╦ūóX/Y×ķ▐D(zhu©Żn)ōQŚl╝■Ż¼X×ķ▐D(zhu©Żn)ōQŪ░▌ö╚ļūā┴┐Ą─╚ĪųĄŻ¼ Y×ķ▌ö│÷ųĄŻ¼ė╔ė┌▒Š└²ø]ėą▌ö╚ļūā┴┐Ż¼╣╩X╬┤ś╦╔ŽöĄ(sh©┤)ųĄĪŻ

ĪĪĪĪ2Ż«═¼▓ĮĢrą“▀ē▌ŗļŖ┬ĘĄ─įO(sh©©)ėŗĘĮĘ©

ĪĪĪĪ═¼▓ĮĢrą“▀ē▌ŗļŖ┬ĘĄ─įO(sh©©)ėŗ║═Ęų╬÷š²║├ŽÓĘ┤Ż¼Ė∙ō■(j©┤)ĮoČ©▀ē▌ŗ╣”─▄Ą─ę¬Ū¾Ż¼įO(sh©©)ėŗ═¼▓ĮĢrą“▀ē▌ŗļŖ┬ĘĪŻįO(sh©©)ėŗĄ─ĻP(gu©Īn)µI╩ŪĖ∙ō■(j©┤)įO(sh©©)ėŗę¬Ū¾┤_Č©ĀŅæB(t©żi)▐D(zhu©Żn)ōQĄ─ęÄ(gu©®)┬╔║═Ū¾│÷Ė„ė|░l(f©Ī)Ų„Ą─“ī(q©▒)äėĘĮ│╠ĪŻ

ĘĄ╗žĒö▓┐

ĘĄ╗žĒö▓┐ ╦óą┬Ēō├µ

╦óą┬Ēō├µ Ž┬ĄĮĒōĄū

Ž┬ĄĮĒōĄū