與門(mén)(英語(yǔ):AND gate)又稱(chēng)“與電路”、邏輯“積”、邏輯“與”電路。是執(zhí)行“與”運(yùn)算的基本邏輯門(mén)電路。有多個(gè)輸入端,一個(gè)輸出端。當(dāng)所有的輸入同時(shí)為高電平(邏輯1)時(shí),輸出才為高電平,否則輸出為低電平(邏輯0)。

中文名:與門(mén)

外文名:AND gate

含 義:所有條件必須具備。

表達(dá)式:F=A·B

所屬范圍:邏輯門(mén)

別 名:與電路、邏輯積、邏輯與電路

功 能:執(zhí)行“與”運(yùn)算的基本邏輯門(mén)電路

應(yīng)用學(xué)科:物理等

適用領(lǐng)域:電路、邏輯等

基本功能

與門(mén)是實(shí)現(xiàn)邏輯“乘”運(yùn)算的電路,有兩個(gè)以上輸入端,一個(gè)輸出端(一般電路都只有一個(gè)輸出端,ECL電路則有二個(gè)輸出端)。只有當(dāng)所有輸入端都是高電平(邏輯“1”)時(shí),該電路輸出才是高電平(邏輯“1”),否則輸出為低電平(邏輯“0”)。 其二輸入與門(mén)的數(shù)學(xué)邏輯表達(dá)式:Y = AB,對(duì)應(yīng)的真值表如下:

邏輯符號(hào)

與門(mén)有3種邏輯符號(hào),包括:形狀特征型符號(hào)(ANSI/IEEEStd 91-1984)、IEC矩形國(guó)標(biāo)符號(hào)(IEC 60617-12)、DIN符號(hào)(DIN 40700)。

實(shí)現(xiàn)

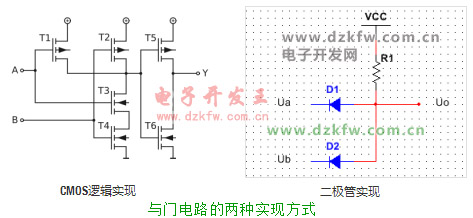

與門(mén)的實(shí)現(xiàn)方法包括使用CMOS邏輯、NMOS邏輯、PMOS邏輯以及二極管實(shí)現(xiàn)等。

以二極管實(shí)現(xiàn)為例,與門(mén)的實(shí)現(xiàn)原理為:

如圖:為二極管與門(mén)電路,Vcc = 5v,R1 = 3K9, 假設(shè)3v及以上代表高電平,0.7及以下代表低電平,

下面根據(jù)圖中情況具體分析一下,

1. Ua=Ub=0v時(shí),D1,D2正向偏置,兩個(gè)二極管均會(huì)導(dǎo)通,此時(shí)Uo為電位為0.7v.,輸出為低電平

2.當(dāng)Ua,Ub一高一低時(shí),不妨假設(shè)Ua = 3v,Ub = 0v,這時(shí)我們不妨先從D2開(kāi)始分析,

D2會(huì)導(dǎo)通,導(dǎo)通后D2壓降將會(huì)被限制在0.7v,那么D1由于右邊是0.7v左邊是3v所以會(huì)反向偏置而截止,因此最后Uo為0.7v低電平輸出,這里也可以從D1開(kāi)始分析,如果D1導(dǎo)通,那么Uo應(yīng)當(dāng)為3.7v,

此時(shí)D2將導(dǎo)通,那么D2導(dǎo)通,壓降又會(huì)變回0.7,最終狀態(tài)Uo仍然是0.7v.輸出低電平,此時(shí)D1馬上截止。

3. Va=Vb=3v,這個(gè)情況很好理解, D1,D2都會(huì)正偏,Uy被限定在3.7V.

總結(jié)(借用個(gè)定義):通常二極管導(dǎo)通之后,如果其陰極電位是不變的,那么就把它的陽(yáng)極電位固定在比陰極高0.7V的電位上;如果其陽(yáng)極電位是不變的,那么就把它的陰極電位固定在比陽(yáng)極低0.7V的電位上,人們把導(dǎo)通后二極管的這種作用叫做鉗位。(特別說(shuō)明:壓差大的二極管先導(dǎo)通,先鉗位,先導(dǎo)通的二極管具有電路控制權(quán))

集成電路

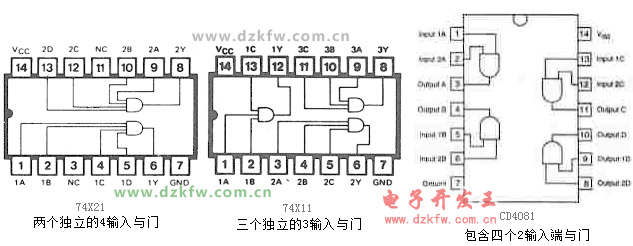

與門(mén)是基本的邏輯門(mén),因此在TTL和CMOS集成電路中都是可以使用的。標(biāo)準(zhǔn)的74系列CMOS集成電路有74X08、74X09(OC),包含四個(gè)獨(dú)立的2輸入與門(mén);74X11,包含三個(gè)獨(dú)立的3輸入與門(mén);74X21,包含兩個(gè)獨(dú)立的4輸入與門(mén)。CD4000系列集成電路有:CD4081,包含四個(gè)2輸入端與門(mén);CD4082,包含兩個(gè)4輸入端與門(mén)。 引腳分配如下:

返回頂部

返回頂部 刷新頁(yè)面

刷新頁(yè)面 下到頁(yè)底

下到頁(yè)底